Altera 28nm FPGA Stratix V GX器件高速串行接口最高支持14.1Gbps(GT器件支持28.5Gbps),Pcie协议hard ip core支持Gen1/2/3。Pcie Gen3 8Gbps/lane使之在数据采集和网络传输领域拥有广泛的应用。高速Pcie Gen3通讯接合Altera FPGA Open CL,在大数据存储、处理和数据挖掘应用领域中如虎添翼,必然游刃有余。

为此,我们在Pcie协议和Altera Pcie ip core应用上投入了很多。Altera Stratix V GX在Pcie上拥有灵活的架构和可靠的性能,在最近设计的Stratix V GX前期验证平台板上测试通过了14.1Gbps的串行速率,现在又测试通过了Pcie Gen3协议,性能稳定可靠。分享一下到达目标的快乐,上图:

开发场地 ,三台机器,一台45nm,一台32nm,最新的是22nm的,基本是最高配置。图上看到只有两台,最早的一台功耗大、工作噪音大被流放到旁边去了。在这个环境上做过双机设备Pcie互联通讯,比10Gbps网络快了一倍多(去年做的,用Qsfp电缆连接的)。

机器被开堂破肚,不折腾就做不了技术活。图中鼠标前接满Sma缆线的板用来测试pcie接口通道,在这次测试Pcie Gen3接口时作用巨大,可以事先确认每个通道的信号质量,实际测试时10Gbps都没问题,何况8Gbps呢,所以如果测试中遇到问题,只有逻辑工程做的不对,避免遇到问题时把原因归结到不可操作的地方。

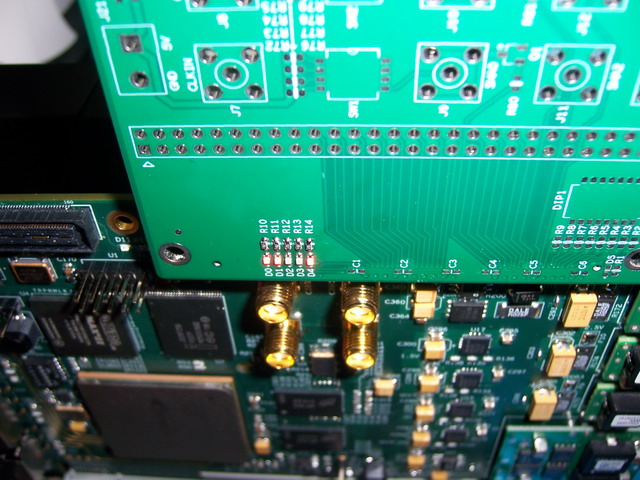

Stratix V GX测试板插到系统机箱内,为方便测试,在hsmc插座上插了块有led、sma接口、一般io接口的扩展板,需要测试的信号可被引到上部,这样不致于拿着仪器探头费劲的去测量相关信号,避免一不小心碰出火花报废主板

事先把PCIE Gen3测试工程烧写到配置芯片中,FPP X16配置方式非常快,Straitx V GX的Pcie Gen3 核在链路训练阶段根据数据通道的特性握手协商具体工作的通道 数量和速率,我们必需有技术手段检测实际工作的通道数和通道速率。为此,我们在硬件工程中把currentSpeed[1:0]信号引出到led中显示。显示01--2.5G 10--5.0G 11--8G。OK,上电后,我们发现LED最左边的两位显示11,表明PCIE Gen3链路协商通过了,这是硬件逻辑端看到的结果(后面我们从主机系统内看设备配置空间中的链路状态寄存器,同样可以判断链路协商结果)。

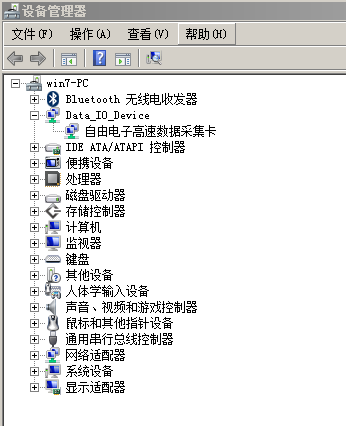

系统中检测到设备,为板卡准备驱动程序必不可少,安装好驱动,然后再开发应用层软件,就可以测试板卡了。设备被识别和驱动安装完毕是一个阶段性成果。

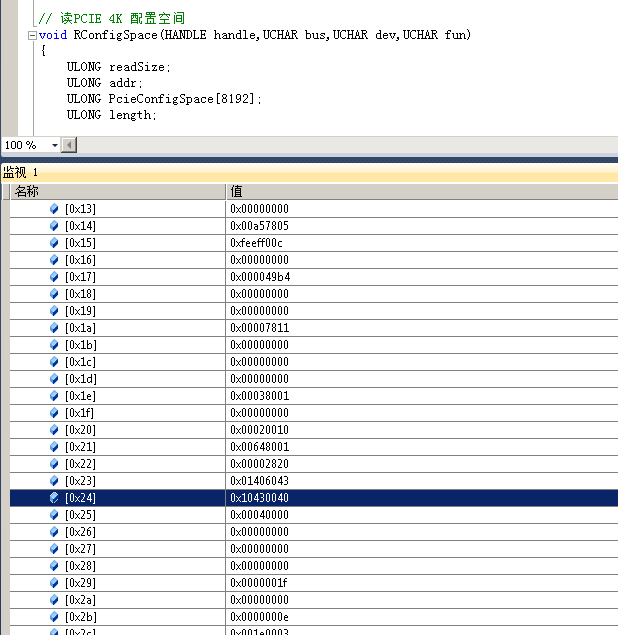

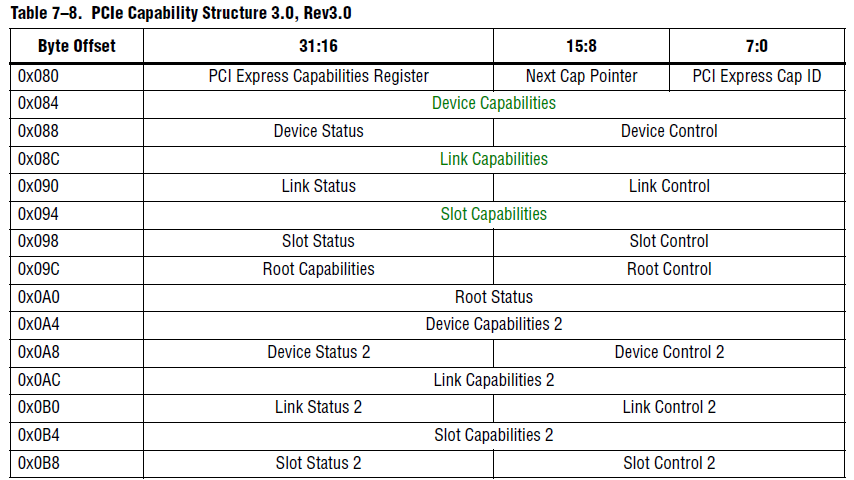

前面,我们已经通过在板上逻辑引出速率信号,显示在LED上,但只显示了通道速率,还有很多Pcie设备相关信息和判读需要通过主机系统读取设备中的configSpace信息来实现。为此,我们在应用程序和驱动程序中增加了读取设备配置空间的代码和功能。见下图,在Pci Express功能寄存器组中(PCI Express Capability Structure),通过链路 状态寄存器,我们可以判读出,系统训练结果是4个通道,Gen3速率。

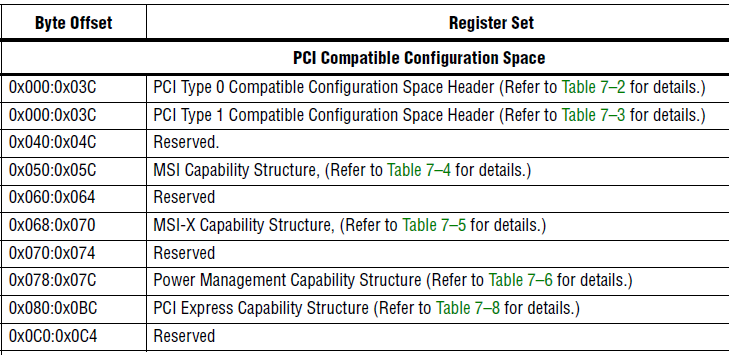

下图可以帮助大家理解Pcie 配制空间的地址(注意上图中是Dword地址排序,所以和下图相差4倍,0x080是PCI Express Capability Structure地址,在上图中是0x20)

其中链路状态寄存器在0x90(我们读出的数据0x24的高两字节处:0x1043:解读为最低四位(3-0)链路速率,9-4链路协商后通道数,0X1043表示4通道,Gen3 8Gbps速率)。

至此,Altera Stratix V Gx pcie Gen3设备在系统中已经顺利装载,我们可以进入后续应用开发中了。

Altera Stratix V Gx器件不单支持Pcie Gen3应用设备,其灵活的模块化结构适应Pcie Gen3协议 ip core的验证,器件支持PIPE 3.0接口,能方便的让ASIC开发验证工程师实现自主知识产权的PCIE Gen3 IP CORE设计和研发。 |